��Ԕ����FPGAоƬ���x(�D��)

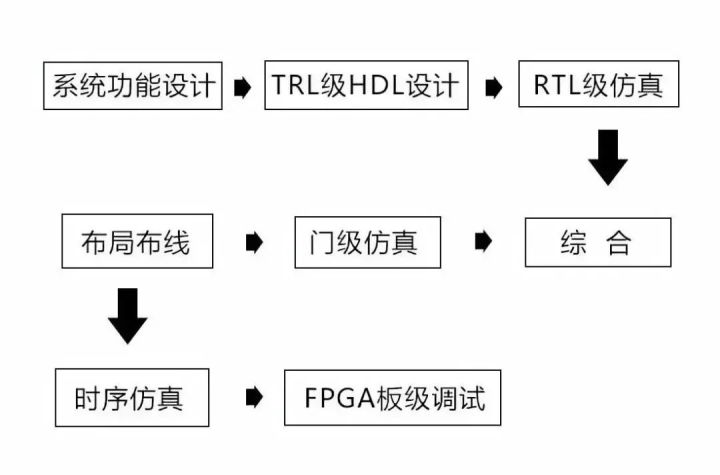

FPGA�_�l(f��)����

ԭ��D��HDL��Hardware DescriptiIon Language��Ӳ�������Z�ԣ��ǃɷN��õĔ�(sh��)��Ӳ���·��������������HDL�O(sh��)Ӌ�����и��õĿ���ֲ�ԡ�ͨ���Ժ�ģ�K�����c�����Ե����c����Ŀǰ�Ĺ����O(sh��)Ӌ�б��V��ʹ�ã����挦FPGA�O(sh��)Ӌ��Ϥ�·�r���_�l(f��)�����ǻ���HDL�ġ�

1.ϵ�y(t��ng)�����O(sh��)Ӌ

��ϵ�y(t��ng)�O(sh��)Ӌ֮ǰ������Ҫ�M�е��Ƿ���Փ�C��ϵ�y(t��ng)�O(sh��)Ӌ��FPGAоƬ�x��Ȝ�(zh��n)�乤����ϵ�y(t��ng)���̎�����(j��)�΄�(w��)Ҫ����ϵ�y(t��ng)��ָ��(bi��o)�͏�(f��)�s�ȣ��������ٶȺ�оƬ�����ĸ��N�YԴ���ɱ��ȷ����M�Й�(qu��n)�⣬�x��������O(sh��)Ӌ�����ͺ��m��������͡�һ�㶼����������µ��O(sh��)Ӌ��������ϵ�y(t��ng)�ֳ����ɂ�������Ԫ��Ȼ���ٰ�ÿ��������Ԫ���֞���һ�ӴεĻ�����Ԫ��һֱ�@������ȥ��ֱ������ֱ��ʹ��EDAԪ�����ֹ��

2.RTL��HDL�O(sh��)Ӌ

RTL����RegisterTransferLevel���Ĵ�����ݔ����ָ���P(gu��n)ע�Ĵ����ͽM��߉�ļ���(ji��)����ʹ���˶��ق�߉�T��߉�T���B���ؓ�Y(ji��)��(g��u)�ȣ���ͨ�^������(sh��)��(j��)�ڼĴ���֮�g�����Ӻ����̎���������@Щ��(sh��)��(j��)���ӵ�ģ�͵�HDL�O(sh��)Ӌ������RTL�����T��������ͬ�rҲ�����κ�Ч��RTL����������c�ǿ���ֱ���þC�Ϲ��ߌ���C�ϳɞ��T���W(w��ng)��������RTL���O(sh��)Ӌֱ�ӛQ����ϵ�y(t��ng)�Ĺ��ܺ�Ч�ʡ�

3.RTL������

Ҳ�Q�鹦�ܣ��О飩���棬���ǾC��ǰ���棬���ھ��g֮ǰ���Ñ����O(sh��)Ӌ���·�M��߉������C���˕r�ķ���]�����t��Ϣ���H�������Ĺ����M�Йz�y������ǰ��Ҫ�����ò��ξ�����HDL�Ƚ��������ļ��͜yԇ�������������P(gu��n)�ĵ�ݔ����̖�M�ϳ����У�������Y(ji��)���������Ɉ���ļ���ݔ����̖���Σ����б�����^�������(ji��)�c��̖��׃��������l(f��)�F(xi��n)�e�`���t�����O(sh��)Ӌ��߉�O(sh��)Ӌ��

���õĹ�����ModelTech��˾��ModelSim��Sysnopsys��˾��VCS��Cadence��˾��NC-Verilog�Լ�NC-VHDL��ܛ�����mȻ���ܷ��治��FPGA�_�l(f��)�^���еı��貽�E�����s��ϵ�y(t��ng)�O(sh��)Ӌ�����P(gu��n)�I��һ����

������߹��ܷ����Ч�ʣ���Ҫ�����yԇƽ�_testbench����yԇ����һ��ʹ���О鼉HDL�Z������������RTL��ģ�K�ǿɾC�ϵģ������О鼉ģ�K��һ���Ӽ��ϡ�

4.�C��

���^�C�Ͼ��nj��^������Ӵε������D(zhu��n)�����^�͌Ӵε��������C�σ�(y��u)������(j��)Ŀ��(bi��o)�cҪ��(y��u)�������ɵ�߉�B�ӣ�ʹ�Ӵ��O(sh��)Ӌ ƽ�滯����FPGA���ֲ���ܛ���M�Ќ��F(xi��n)����Ŀǰ�ČӴ������C�σ�(y��u)����Synthesis����ָ���O(sh��)Ӌݔ�뾎�g�����c�T�����T�����T��RAM���|�l(f��)���Ȼ���߉��Ԫ�M�ɵ�߉�B�ӾW(w��ng)�����������挍���T���·��

�挍���w���T���·��Ҫ����FPGA�����̵IJ��ֲ������ܣ�����(j��)�C�Ϻ����ɵĘ�(bi��o)��(zh��n)�T���Y(ji��)��(g��u)�W(w��ng)����a(ch��n)�����������D(zhu��n)�Q�ɘ�(bi��o)��(zh��n)���T���Y(ji��)��(g��u)�W(w��ng)����HDL����ľ�����횷����ض��C������Ҫ����L(f��ng)�������T���Y(ji��)��(g��u)��RTL����HDL����ľC���Ǻܳ���ļ��g(sh��)�����еľC����������֧�ֵ��@һ���e�ľC�ϡ����õľC�Ϲ�����Synplicity��˾��Synplify/SynplifyProܛ���Լ�����FPGA�S���Լ��Ƴ��ľC���_�l(f��)���ߡ�

5.�T������

Ҳ�Q��C�Ϻ���棬�C�Ϻ����z��C�ϽY(ji��)���Ƿ��ԭ�O(sh��)Ӌһ�¡��ڷ���r���ѾC�����ɵĘ�(bi��o)��(zh��n)�ӕr�ļ�����(bi��o)ע���C�Ϸ���ģ����ȥ���ɹ�Ӌ�T�ӕr������Ӱ푡� ���@һ���E���ܹ�Ӌ���ӕr����˺Ͳ�����Č��H��r߀��һ���IJ�࣬����ʮ�֜�(zh��n)�_��

Ŀǰ�ľC�Ϲ����^����죬����һ����O(sh��)Ӌ����ʡ���@һ����������ڲ��ֲ�����l(f��)�F(xi��n)�·�Y(ji��)��(g��u)���O(sh��)Ӌ��D�������t��Ҫ���ݵ��C�Ϻ������_�J(r��n)���}֮���ڡ��ڹ��ܷ����н�B��ܛ������һ�㶼֧�־C�Ϻ���档

6.���ֲ���

���F(xi��n)�nj��C�����ɵ�߉�W(w��ng)�����õ����w��FPGAоƬ�ϣ������̵�߉�͕r���c�����Ŀ����YԴƥ�䡣���ֲ�������������Ҫ���^�̣�����߉�W(w��ng)���е�Ӳ��ԭ�Z�͵ӆ�Ԫ���������õ�оƬ��(n��i)���Ĺ���Ӳ���Y(ji��)��(g��u)�ϣ�����������Ҫ���ٶ��(y��u)����e�(y��u)֮�g�����x��

��������(j��)���ֵ��ؓ�Y(ji��)��(g��u)������оƬ��(n��i)���ĸ��N�B���YԴ���������_���B�Ӹ���Ԫ����Ҳ���Ժ��ε،����ֲ�������錦FPGA��(n��i)�����ұ��ͼĴ����YԴ�ĺ������ã����ֿ��Ա��������x�Ɍ��F(xi��n)�O(sh��)Ӌ�W(w��ng)�����(y��u)���YԴ�M�ϣ����������nj��@Щ���ұ��ͼĴ����YԴ���(y��u)��ʽ�B��������

Ŀǰ��F(xi��n)PGA�ĽY(ji��)��(g��u)�dz���(f��)�s���e�����Еr��s���l���r����Ҫ���Õr���(q��)�ӵ������M�в��ֲ����������Y(ji��)����ܛ�����ߕ��Ԅ����Ɉ�棬�ṩ���P(gu��n)�O(sh��)Ӌ�и������YԴ��ʹ����r������ֻ��FPGAоƬ���a(ch��n)�̌�оƬ�Y(ji��)��(g��u)����˽⣬���Բ��ֲ�������x��оƬ�_�l(f��)���ṩ�Ĺ��ߡ�

7.�r�����

��ָ�����ֲ������ӕr��Ϣ����(bi��o)ע���O(sh��)Ӌ�W(w��ng)���Ё�z�y�Пo�r���`Ҏ(gu��)�������M��r��s���l�����������еĕr��Ҏ(gu��)�t���罨���r�g�����֕r�g�ȣ��F(xi��n)�r����� ���������t��Ϣ��ȫ��Ҳ��_�����^�õط�ӳоƬ�Č��H������r��

���ڲ�ͬоƬ�ă�(n��i)���ӕr��һ�ӣ���ͬ�IJ��ֲ�������Ҳ�o�ӕr������ͬ��Ӱ푡�����ڲ��ֲ�����ͨ�^��ϵ�y(t��ng)����ģ�K�M�Еr����棬������r���P(gu��n)ϵ����Ӌϵ�y(t��ng)���ܣ��Լ��z�����������ð�U�Ƿdz��б�Ҫ�ġ�

8.FPGA�弉�{(di��o)ԇ

ͨ�^�����������ֲ�����������ļ����d��FPGA�У�����Ӳ���M�о��̡������ļ�һ���.pof��.sof�ļ���ʽ�����d�ķ�ʽ����AS�����ӣ���PS�����ӣ���JTAG��߅����裩�ȷ�ʽ��

߉�����x��LogicAnalyzer��LA����FPGA�O(sh��)Ӌ����Ҫ�{(di��o)ԇ���ߣ�����Ҫ���������Ĝyԇ���_����LA�r���F��Ŀǰ��������FPGAоƬ���a(ch��n)�̶��ṩ�˃�(n��i)Ƕ���ھ�߉�����x����XilinxISE�е�ChipScope��AlteraQuartusII�е�SignalTapII�Լ�SignalProb������Q����ì�ܣ�����ֻ��Ҫռ��оƬ������߉�YԴ�����кܸߵČ��Ãrֵ��

FPGA��ʲô�@ô�y��

�mȻ��“�f��оƬ”�����u������FPGA��ȫ����(n��i)�Ј�Ҏ(gu��)ģ߀�dz����ޣ��h����CPU��GPU�Ј�Ҏ(gu��)ģ������@һ�N�F(xi��n)���ԭ������Ҫ��FPGA�ИI(y��)�T���dz��ߡ�

����(j��)Gartner��(sh��)��(j��)�@ʾ��2015����2020��ȫ��FPGA�Ј������(f��)�����L�ʞ�9%����2020��ȫ��FPGA �Ј�Ҏ(gu��)ģ���_84�|�������@�ӵ��Ј��h(hu��n)���£���I(y��)��Ҫ������ȥ���y�̶ȿ����֪���e�����^���ć���(n��i)��I(y��)��

����ؿ���l(f��)չ�v�̣���1984��Xilinx��(chu��ng)���FPGA֮���Ⱥ����ϰټ��ИI(y��)���^�������@һ�I(l��ng)����K�ĽY(ji��)���_���^����I(y��)���|����w������Intel��Philips��Agere Systems��AMD�Լ�Ħ���_���ȇ��H֪����оƬ�O(sh��)Ӌ�S�̡��܉��Ҵ����Ď���I(y��)���@�Ï������F�ˡ�

�����ڇ���(n��i)FPGA��I(y��)���ԣ��ڳ����A�ο��ܶ������ٽ��b�ˇ���a(ch��n)Ʒ��������Ҫ���a(ch��n)Ʒ��Ҏ(gu��)ģ�����Ј����ͱ�����R���g(sh��)�������}�����H�ϣ�������I(y��)�ѽ�(j��ng)�Ŕ��˽^�������g(sh��)������(n��i)�S����Ҫ�M�룬���Ⱦͱ���Լ������_�l(f��)оƬ�Y(ji��)��(g��u)�����⌣���֙�(qu��n)���@���ڇ���(n��i)��I(y��)���ԟo����һ��������(zh��n)��

����оƬ�ܘ�(g��u)֮�⣬��FPGA�_�l(f��)�^�������漰���ķ��湤��֮ǰһֱ��ه�M�ڣ��@���ڇ���(n��i)��I(y��)���ԟo��������һ헷dz��������(zh��n)����Ҫ����(n��i)�S����Ӳ����ܛ���ɷ�����m(x��)����Ͷ�롣Ŀǰ������(n��i)�S����ܛ�����棬Ҳ�����cͻ�ƣ������ѽ�(j��ng)ȡ����һЩ�ɿ���

���⣬����ǰ�����ԣ�F(xi��n)PGA��һ���T���dz��ߵ��ИI(y��)�����Ј��ƏV�^���У�ԭ�S��Ҫ���͑��M�Ќ��I(y��)ָ��(d��o)���@�o����Ҳ����������Ʒ�Ʈa(ch��n)Ʒ��Q���y�ȡ��ɴ�Ҳ��(d��o)���ˣ�F(xi��n)PGA�a(ch��n)Ʒ����?li��n)Q���l�ʱ��^�ͣ��Ј����gҲ�y������X�������֙C�ȳ��F(xi��n)����w�S���ݣ�Դ��늣��ӣ��W(w��ng)�������ṩ���g(sh��)֧��

���ĵ�ַ��http://www.189yp.com/dz/22/15486810413124.shtml

����(bi��o)��:

- ��һƪ���£���Ƭ�CҪ�@ô�W(xu��)���˗l֔(j��n)ӛ!

- ��һƪ���£���ܱ��Ԅәz�yϵ�y(t��ng)��ԭ�����O(sh��)Ӌ(�D��)

-

���� | �ɾ��̾���оƬ�ׂ�֪�R�c

���� | �ɾ��̾���оƬ�ׂ�֪�R�c

ʲô�ǿɾ��̾��ɾ��̾��������Դ�����Ƀɂ�оƬ�M�ɣ�һ����ȫ��MEMS�C������һ���Ǿ��М��a���ܵ�оƬ�����Ԇ����·�i��h(hu��n)CMOS�������Ø�(bi��o)��(zh��n)���İ댧(d��o)�wоƬMCM���b�����Բ���ȫ�ԄӘ�(bi��o)��(zh��n)�댧(d��o)�w���칤ˇ

�P(gu��n)�I�~�� ���ٙ�Ŀ����ӻ��A(ch��) -

���I(y��)���C��Q����������16λ��(sh��)ģ�D(zhu��n)�QоƬ+ؓ�����Է�(w��n)

���I(y��)���C��Q����������16λ��(sh��)ģ�D(zhu��n)�QоƬ+ؓ�����Է�(w��n)

�ڹ��I(y��)���C�ИI(y��)�У�ʯӢ�ɾ��̾�����������P(gu��n)��Ҫ�Ľ�ɫ�����˝M�㲻ͬ��(y��ng)������YXC�����˵Ͷ���ʯӢ�ɾ��̾���QMEMS��ʎ��YSO690PR���鹤�I(y��)���C�ķ�(w��n)���\���ṩ�������Q������

�P(gu��n)�I�~�� ���ٙ�Ŀ����ӻ��A(ch��) -

PL2733A ������ͬ������������

PL2733A ������ͬ������������

�P(gu��n)�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

PL5358 ��늳���x��/�ۺ���늳ر��o�����·

PL5358 ��늳���x��/�ۺ���늳ر��o�����·

�P(gu��n)�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

PL2303 PFM���� DC-DC ׃�Q��

PL2303 PFM���� DC-DC ׃�Q��

�P(gu��n)�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

PL5900A 1.2Aͬ�������{(di��o)��(ji��)��

PL5900A 1.2Aͬ�������{(di��o)��(ji��)��

�P(gu��n)�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

PS7516 2.5A��Чͬ��PWM�����D(zhu��n)�Q��

PS7516 2.5A��Чͬ��PWM�����D(zhu��n)�Q��

�P(gu��n)�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

PL7501C �p��(ji��)�늳س�늹���оƬ

PL7501C �p��(ji��)�늳س�늹���оƬ

�P(gu��n)�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

PL7501CL �p��(ji��)�늳س�늹���оƬ

PL7501CL �p��(ji��)�늳س�늹���оƬ

�P(gu��n)�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

PS7526 ��Ч DC-DC ͬ�����������D(zhu��n)�Q��

PS7526 ��Ч DC-DC ͬ�����������D(zhu��n)�Q��

�P(gu��n)�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

PL7512A ��ͬ����PWM�����D(zhu��n)�Q��

PL7512A ��ͬ����PWM�����D(zhu��n)�Q��

�P(gu��n)�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

FP6396 1.2Aͬ�������D(zhu��n)�Q��

FP6396 1.2Aͬ�������D(zhu��n)�Q��

�P(gu��n)�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

FP6378A 2Aͬ�������{(di��o)��(ji��)��

FP6378A 2Aͬ�������{(di��o)��(ji��)��

�P(gu��n)�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

FR9608 3Aͬ������DC/DC�D(zhu��n)�Q��

FR9608 3Aͬ������DC/DC�D(zhu��n)�Q��

�P(gu��n)�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

JD6621 ���ٳ�늅f(xi��)�h��USB-PD 3.0�cPPS������

JD6621 ���ٳ�늅f(xi��)�h��USB-PD 3.0�cPPS������

�P(gu��n)�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

FR9811 2Aͬ������DC/DC�D(zhu��n)�Q��

FR9811 2Aͬ������DC/DC�D(zhu��n)�Q��

�P(gu��n)�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

FP6601AA USB Type-A ���ٳ�늅f(xi��)�h������

FP6601AA USB Type-A ���ٳ�늅f(xi��)�h������

�P(gu��n)�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

FP6606C USB���-C��PD��늿�����

FP6606C USB���-C��PD��늿�����

�P(gu��n)�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

FP6381A ��Ч1.5MHz 1.2Aͬ������׃�l��

FP6381A ��Ч1.5MHz 1.2Aͬ������׃�l��

�P(gu��n)�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

FP6715 5V��2.5A��550 KHz��Ч�Ͳ��yͬ�������D(zhu��n)�Q��

FP6715 5V��2.5A��550 KHz��Ч�Ͳ��yͬ�������D(zhu��n)�Q��

�P(gu��n)�I�~�� ���ٙ�Ŀ��Ԫ����֪�R

������dȤ��

- ���]��(n��i)��

- ����(n��i)��

-

- ��ֿɾ�����ʎ�����l�c50MHz��LVDSݔ������(y��ng)������ҕ�l̎���� 2024-06-11

- YXC��ԴʯӢ���w��ʎ�����l�c24MHz��3225���b����(y��ng)�������ܔz���^ 2024-06-07

- �ɾ�����ʎ�����l�c125MHz��3225���b����(y��ng)����ҕ�l�K�� 2024-06-06

- 24MHz܇Ҏ(gu��)�C������ؓ�d8PF�������ض�-40~125�棬��(y��ng)����܇�����-TMCU���� 2024-06-05

- YXCʯӢ��ʎ�����l�c16MHz������늉�1.8V-3.3V����(y��ng)���ڰ������� 2024-06-04

- YXC��ԴʯӢ���w��ʎ�����l�c25MHz�����b2016����(y��ng)������ӟ� 2024-05-28

- YXC�ɾ�����ʎ�����l�c100MHz������늉�3.3V����(y��ng)���ڹPӛ����X 2024-05-27

- YXC܇Ҏ(gu��)�C���� 8MHz��ؓ�d20PF�������ض�-40~125�棬��(y��ng)����܇�d��܇?y��n)��_ 2024-05-23

- YXC�ɾ��̾����l�c10.48576MHz�����b5032����(y��ng)���ڹ�˙C 2024-05-22

- YXC�ɾ��̲����ʎ�����l�c50MHz��7050���b��LVDSݔ������(y��ng)���ڼ���y���x 2024-05-20

- ���T��(bi��o)��

-

���ż����· ������·�D LED ���l�Ŵ����·�D ��Ƭ�C 늙C���� LED�·�D ��(w��n)���Դ �_�P(gu��n)��(w��n)���Դ ����·�D ׃�l�� ��׃�� LED�����· ���{(di��o)�S���g(sh��) LED�(q��)���·�D AV�Ŵ����· �ص����·�D 555���r�� 늴Št�·�D ��(w��n)�������· 51��Ƭ�C �·�O(sh��)Ӌ �^�����o�· �^�����o�· ��(w��n)���· �ھ�Ӌ�� ���˷�(w��n)���· ��·���o�· �ŷ�늙C ���M늙C PIC��Ƭ�C ֱ����(w��n)���Դ ���{(di��o)��(w��n)���Դ EMC ©늱��o�· Ƕ��ʽϵ�y(t��ng) ��Ȧ ���l��׃�� ���� ���{(di��o) UPS DC-DC�· �ضȂ����� 늴ż��� ���� ���l�_�P(gu��n)�Դ ���� EMI ��˹�� ���⾀