��Ԕ����FPGAоƬ���x(�D��)

���գ���ý�w����Q��������Ӽ��g�о�����ǰ�ɹ����Ƴ������ׂ������ɿص����ǧ�f�T�������ܸ߿ɿ�FPGA���F���ɾ����T��У�оƬ��

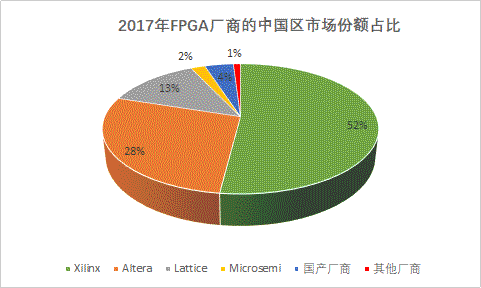

FPGAһֱ�LJ��ȵĶ̰壬�Ј�����������Ŕࡣ���yӋ��2017����ȳ��^100�|Ԫ��FPGA�Ј��У����a��ռ�ʃH��4%��Ŀǰ��ȫ��FPGA�Ј��������Ĵ���^�ŔࣺXilinx��ِ�`˼����Intel��Ӣ�ؠ�����ǰ��ُ��Altera����Lattice���R��˼����Microsemi(����ɭ��)������FPGA�S���и��ư댧�w�����R�����Ϻ���·���Ϲ�ͬ����AGM���Ϻ��͵��ȡ�

���Ϲ�ͬ��

�S�����M��Ӻ�ͨ�ŵȽK���O�������������L���˹����ܡ�������Ӌ�㡢������܇�Լ����W߅��Ӌ��İlչ����FPGA������Ҳ�������������CPU��GPU��FPGA�����V�������֪�������҂�Ҳ�������ν�B���@һ“�f��оƬ”��

ʲô��FPGA��

FPGA��Ӣ��Field Programmable Gate Array�Ŀs�������F���ɾ����T��У�������PAL��GAL��EPLD�ȿɾ��������Ļ��A���Mһ���lչ�Įa��������錣�������·��ASIC���I���е�һ�N�붨���·�����F�ģ��Ƚ�Q�˶����·�IJ��㣬�ֿ˷���ԭ�пɾ��������T�·������ȱ�c��

FPGA����С�Ͳ��ұ���16×1RAM���팍�F�M��߉��ÿ�����ұ��B�ӵ�һ��D�|�l����ݔ��ˣ��|�l���ف�������߉�·����I/O���ɴ˘����˼ȿɌ��F�M��߉�����ֿɌ��F�r��߉���ܵĻ���߉��Ԫģ�K���@Щģ�K�g���ý����B�������B�ӻ��B�ӵ�I/Oģ�K��

FPGA��߉��ͨ�^��Ȳ��o�B�惦��Ԫ���d���̔����팍�F�ģ��惦�ڴ惦����Ԫ�е�ֵ�Q����߉��Ԫ��߉�����Լ���ģ�K֮�g��ģ�K�cI/O�g���ӷ�ʽ������K�Q����FPGA���܌��F�Ĺ��ܣ�FPGA���S�o�εľ��̡�

FPGA�����c

1.����FPGA�OӋASIC�·�����ü����·�����Ñ�����ҪͶƬ���a�����ܵõ����õ�оƬ��

2.FPGA��������ȫ���ƻ�붨��ASIC�·����ԇ��Ƭ��

3.FPGA�Ȳ����S�����|�l����I/O���_��

4.FPGA��ASIC�·���OӋ������̡��_�l�M����͡��L�U��С������֮һ��

5.FPGA���ø���CMOS��ˇ�����ĵͣ������cCMOS��TTL�ƽ���ݡ�

FPGA���̼��g

Ŀǰ���Ј��������N������FPGA���̼��g��SRAM�����۽z��Flash�����У�SRAM�������ֹ���÷�����V�ļܘ�����Ҫ������ٶȿ��Ҿ��п��ؾ��������������۽zFPGAֻ����һ�οɾ�������������Flash��FPGA�DZ��^�µļ��g��Ҳ���ṩ���ؾ��̹��ܡ�

����SRAM��FPGA������������һЩ�����ijɱ�����������PROMS֧�ְ�ȫ�ͱ��ܑ��õĂ���늳صȡ�����Flash�ͷ��۽z��FPGA�]���@Щ�[���ɱ�����˿ɱ��C�^�͵Ŀ�ϵ�y�ɱ���

1.����SRAM��FPGA

�@aƷ�ǻ���SRAM�Y���Ŀ���������������ͨ늕rҪ�����Ô����x��Ƭ��SRAM�У�������ɾͿ��M�빤����B����늺�SRAM�е����Ô����Gʧ��FPGA�Ȳ�߉�P�CҲ�S֮��ʧ���@�N����SRAM��FPGA�ɷ���ʹ�á�

2.���۽zFPGA

���÷��۽z���̼��g��FPGA�Ȳ����з��۽z����_�P�Y������߉���ܵĶ��x�Ɍ��þ����������OӋ���F���o���Ĕ����ļ�������Ȳ����۽z�����M�П�䛣��Ķ�ʹ�������F������߉���ܡ�

�@�N������ȱ�c��ֻ��һ���Ծ��̣����c�Ǿ��и߿��ɔ_�Ժ͵��ģ��m����Ҫ��߿ɿ��ԡ��߱����ԵĶ��ͮaƷ��

3.����Flash��FPGA

���@�FPGA�����м�����SRAM�ͷ���ʧ��EEPROM��惦�Y��������SRAM�������������������r��ϵ�y�M�п��ƣ���EEPROM�t�Á��b�dSRAM�������@�FPGA��EEPROM�����ڻ���SRAM��ˇ�ĬF���ɾ������У�������Գ�ְl�]EEPROM�ķ���ʧ�Ժ�SRAM���������ԡ�

��늺�������Ϣ������Ƭ�ȵ�EEPROM�أ���˲���ҪƬ�������оƬ�������ڽ���ϵ�y�ɱ�������OӋ�İ�ȫ�ԡ�

FPGAоƬ�Y��

FPGAоƬ��Ҫ�������ֽM�ɣ��քe��IOE��inputoutputelement��ݔ��ݔ����Ԫ����LAB��logicarrayblock��߉��ЉK������Xilinx�Q֮�������߉�KCLB����Interconnect���Ȳ��B�Ӿ�����

1.IOE

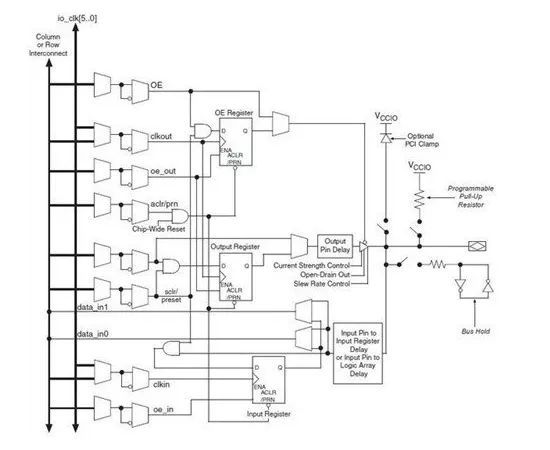

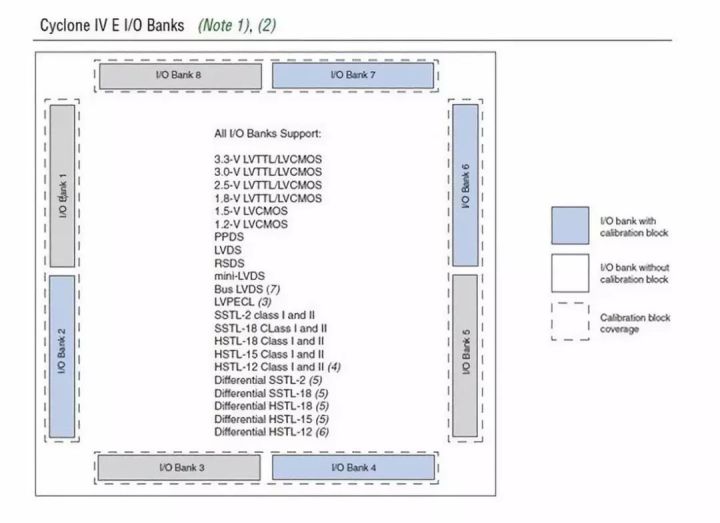

IOE��оƬ�c�ⲿ�·�������ӿڣ���Ҫ��ɲ�ͬ늚�������ݔ��/ݔ����̖�����cƥ��Ҫ����Ļ�����LVTTL/LVCMOS�ӿڵ�PCI/LVDS/RSDS�������N���ӵIJ�ֽӿڣ���5V���ݵ�3.3V/2.5V/1.8V/1.5V���ƽ�ӿڣ�������ALTERA��˾��CycloneIVEP4CE115F29�O���IOE�Y����

FPGA��IOE���M���ÿ�M���܉�����֧�ֲ�ͬ��I/O�˜ʣ�ͨ�^ܛ�����`�����ã���ƥ�䲻ͬ������˜��cIO�������ԣ����ҿ����{��������Ĵ�С�����Ը�׃��/������裬CycloneIV�O����8��IOblank���M����Ҋ�D��

2.LAB

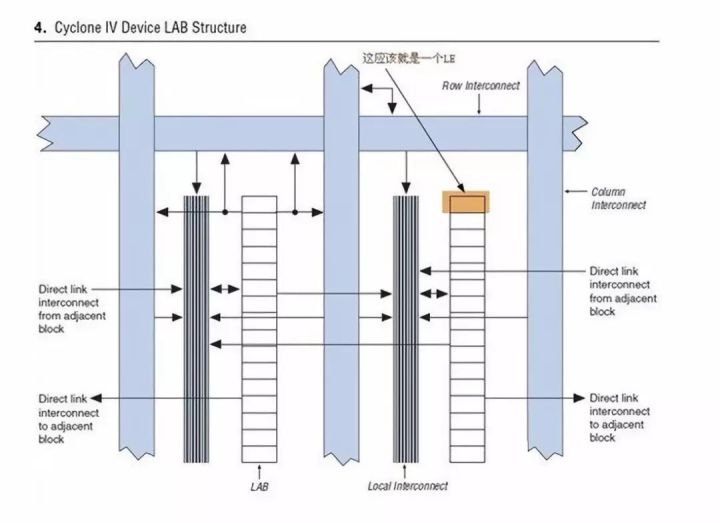

LAB��FPGA�Ļ���߉��Ԫ���䌍�H�Ĕ������������������õ������IJ�ͬ����ͬ��EP4CE115F29�O���ÿ��LAB�IJ��ְ���16��LE��LAB������̖��LEcarrychains��Registerchains��Localinterconnect����LAB�Y���D���£�

LE��CycloneIV�O����С��߉��Ԫ��ÿ��LE��Ҫ��LUT���Ĵ����M�ɵġ�

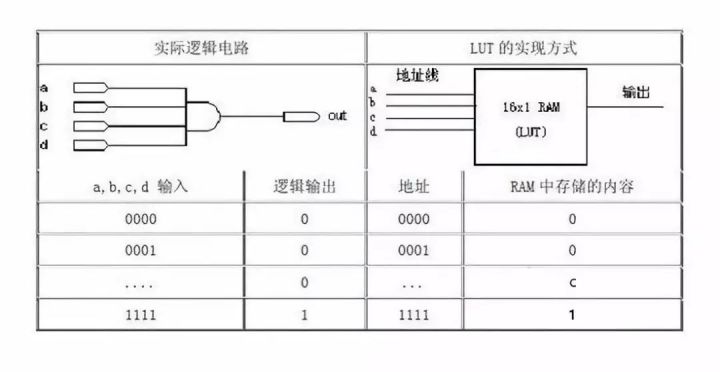

���ұ�LUT��Look-Up-Table���䱾�|��һ���o�B�惦��SRAM��ĿǰFPGA�����4ݔ���LUT��ÿ��LUT���Կ���һ����4λ��ַ����16x1��RAM�����҂�ͨ�^ԭ��D��HDL�Z��������һ��߉�·��FPGA�_�lܛ�����Ԅ�Ӌ��߉�·�����п��ܵĽY�������ѽY�����Ȍ���RAM��

�@�ӣ���FPGA�����r��ÿݔ��һ����̖�M��߉�\��͵���ݔ��һ����ַ�M�в�����ҳ���ַ�����ă��ݣ�Ȼ��ݔ����

3.Interconnect

FPGA�Ȳ��B�Ӿ����S�������������փԵ���������Ҫ��Rowinterconnect��columninterconnect��Directlinkinterconnect��Localinterconnect��Registerchaininterconnect���Ĵ���֮�g�B�ӵ��B�Ӿ�����

�Ȳ��B�Ӿ�ͨFPGA�Ȳ������І�Ԫ�����B�����L�Ⱥ�ˇ�Q������̖���B�Ӿ��ϵ��������͂�ݔ�ٶȡ��ڌ��H�_�l�У��OӋ�߲���Ҫֱ���x���B�Ӿ������ֲ��������Ԅӵظ���ݔ��߉�W�����@�ɾC�����ɣ����ؓ�Y���ͼs���l���x���B�Ӿ����Bͨ����߉��Ԫ�����ԣ��ı��|�ρ��f�������YԴ��ʹ�÷������OӋ�ĽY�������к�ֱ�ӡ�ֱ�ӵ��Pϵ���ݣ�Դ��늣��ӣ��W�������ṩ���g֧��

���ĵ�ַ��http://www.189yp.com/dz/22/15486810413124.shtml

���Ę˺�:

- ��һƪ���£���Ƭ�CҪ�@ô�W���˗l֔ӛ!

- ��һƪ���£���ܱ��Ԅәz�yϵ�y��ԭ�����OӋ(�D��)

-

���� | �ɾ��̾���оƬ�ׂ�֪�R�c

���� | �ɾ��̾���оƬ�ׂ�֪�R�c

ʲô�ǿɾ��̾��ɾ��̾��������Դ�����Ƀɂ�оƬ�M�ɣ�һ����ȫ��MEMS�C������һ���Ǿ��М��a���ܵ�оƬ�����Ԇ����·�i��hCMOS�������ؘʻ��İ댧�wоƬMCM���b�����Բ���ȫ�ԄӘ˜ʰ댧�w���칤ˇ

�P�I�~�� ���ٙ�Ŀ����ӻ��A -

���I���C��Q����������16λ��ģ�D�QоƬ+ؓ�����Է�

���I���C��Q����������16λ��ģ�D�QоƬ+ؓ�����Է�

�ڹ��I���C�ИI�У�ʯӢ�ɾ��̾�����������P��Ҫ�Ľ�ɫ�����˝M�㲻ͬ��������YXC�����˵Ͷ���ʯӢ�ɾ��̾���QMEMS��ʎ��YSO690PR���鹤�I���C�ķ����\���ṩ�������Q������

�P�I�~�� ���ٙ�Ŀ����ӻ��A -

PL2733A ������ͬ������������

PL2733A ������ͬ������������

�P�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

PL5358 ��늳���x��/�ۺ���늳ر��o�����·

PL5358 ��늳���x��/�ۺ���늳ر��o�����·

�P�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

PL2303 PFM���� DC-DC ׃�Q��

PL2303 PFM���� DC-DC ׃�Q��

�P�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

PL5900A 1.2Aͬ�������{����

PL5900A 1.2Aͬ�������{����

�P�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

PS7516 2.5A��Чͬ��PWM�����D�Q��

PS7516 2.5A��Чͬ��PWM�����D�Q��

�P�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

PL7501C �p���늳س�늹���оƬ

PL7501C �p���늳س�늹���оƬ

�P�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

PL7501CL �p���늳س�늹���оƬ

PL7501CL �p���늳س�늹���оƬ

�P�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

PS7526 ��Ч DC-DC ͬ�����������D�Q��

PS7526 ��Ч DC-DC ͬ�����������D�Q��

�P�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

PL7512A ��ͬ����PWM�����D�Q��

PL7512A ��ͬ����PWM�����D�Q��

�P�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

FP6396 1.2Aͬ�������D�Q��

FP6396 1.2Aͬ�������D�Q��

�P�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

FP6378A 2Aͬ�������{����

FP6378A 2Aͬ�������{����

�P�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

FR9608 3Aͬ������DC/DC�D�Q��

FR9608 3Aͬ������DC/DC�D�Q��

�P�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

JD6621 ���ٳ�늅f�h��USB-PD 3.0�cPPS������

JD6621 ���ٳ�늅f�h��USB-PD 3.0�cPPS������

�P�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

FR9811 2Aͬ������DC/DC�D�Q��

FR9811 2Aͬ������DC/DC�D�Q��

�P�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

FP6601AA USB Type-A ���ٳ�늅f�h������

FP6601AA USB Type-A ���ٳ�늅f�h������

�P�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

FP6606C USB���-C��PD��늿�����

FP6606C USB���-C��PD��늿�����

�P�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

FP6381A ��Ч1.5MHz 1.2Aͬ������׃�l��

FP6381A ��Ч1.5MHz 1.2Aͬ������׃�l��

�P�I�~�� ���ٙ�Ŀ��Ԫ����֪�R -

FP6715 5V��2.5A��550 KHz��Ч�Ͳ��yͬ�������D�Q��

FP6715 5V��2.5A��550 KHz��Ч�Ͳ��yͬ�������D�Q��

�P�I�~�� ���ٙ�Ŀ��Ԫ����֪�R

������dȤ��

- ������

-

- �oԴ�����x�� 2024-10-10

- ACM6755 ֧��3�������õ�ȫ��������ֱ���oˢ늙C��IC���� 2024-10-09

- YXC�����Q�����������I���C���� 2024-09-27

- ��Դ����͟oԴ����ą^�e 2024-09-24

- ��ģ�K��Ȳ��p����ѕr�lCP-��־��� 2024-09-20

- ���w�C�����Ĺ���ԭ�� 2024-09-19

- YXCʯӢ��Դ��ֿɾ��̾����l�c200MHZ��С���c�ɾ��_����6λ��������5G��վ 2024-09-12

- 70V�͉����{OVP�ֵ���^�����oо-ƽоPW1600 2024-09-05

- YXC�P�d��Դ��Ʒ�l��ح1.2V�����ĕr犽�Q���� 2024-09-05

- YXC�P�d | 32.768KHZ�����x�ͷ��� 2024-09-02

- ���T�˺�

-

���ż����· ������·�D LED ���l�Ŵ����·�D ��Ƭ�C 늙C���� LED�·�D �����Դ �_�P�����Դ ����·�D ׃�l�� ��׃�� LED�����· ���{�S���g LED���·�D AV�Ŵ����· �ص����·�D 555���r�� 늴Št�·�D ���������· 51��Ƭ�C �·�OӋ �^�����o�· �^�����o�· �����· �ھ�Ӌ�� ���˷����· ��·���o�· �ŷ�늙C ���M늙C PIC��Ƭ�C ֱ�������Դ ���{�����Դ EMC ©늱��o�· Ƕ��ʽϵ�y ��Ȧ ���l��׃�� ���� ���{ UPS DC-DC�· �ضȂ����� 늴ż��� ���� ���l�_�P�Դ ���� EMI ��˹�� ���⾀