����FPGA��32λǶ��ʽ̎�����Ľ�Q����

�҂����քe��һ�¿�����IP��(n��i)�˝M����͑�(y��ng)������Ҫ������N��̫�W(w��ng)��ϵ�y(t��ng)�����ӡ�ÿ�N�O(sh��)Ӌ���в�ͬ��ϵ�y(t��ng)�ܘ�(g��u):����̎�������á���̫�W(w��ng) MAC IP�����Լ��惦���ӿڡ����⣬�@Щ����߀ͻ���˿��c�@ЩӲ����ϵ�y(t��ng)���ʹ�õIJ�ͬTCP/IPܛ���f(xi��)�h��������Ӳ����(g��u)��ģ�K��ܛ���Ӷ��ǿɶ��Ƶģ���������Ը���(j��)��(y��ng)�õ���Ҫ���@Щϵ�y(t��ng)�M�����p��

������̫�W(w��ng)��ϵ�y(t��ng)

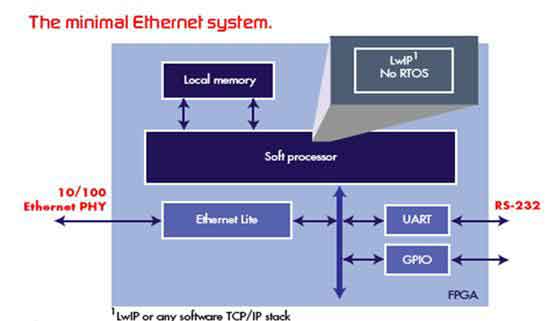

�����h�̱O(ji��n)ҕ����Ƒ�(y��ng)��������Ҫ�ĺ��ξW(w��ng)�j(lu��)�ӿځ��f����D3��ʾ����С���W(w��ng)�j(lu��)��ϵ�y(t��ng)������ˡ��ڴ��(y��ng)���У�TCP/IP����Ҫ���^��(<1Mbps)�����LwIP(�����滥(li��n)�W(w��ng)�f(xi��)�h��)�@�ӵ�СTCP/IP�f(xi��)�h��(����ҪRTOS���r����ϵ�y(t��ng))������ˡ�

�D3��Ҏ(gu��)ģ��С����̫�W(w��ng)ϵ�y(t��ng)��

�@����ʹ�ò��g�����̫�W(w��ng)Lite IP�ں��εIJ�ԃģʽ���F(xi��n)��ȫ��ܛ�����������εđ�(y��ng)�Ìӣ���ȫ���惦��FPGA�еı��ش惦���С���D3����ʾ��������Ҫ��I/O�ӿڣ�RS-232 UART��GPIO���������ӵ�������ϵ�y(t��ng)�С�

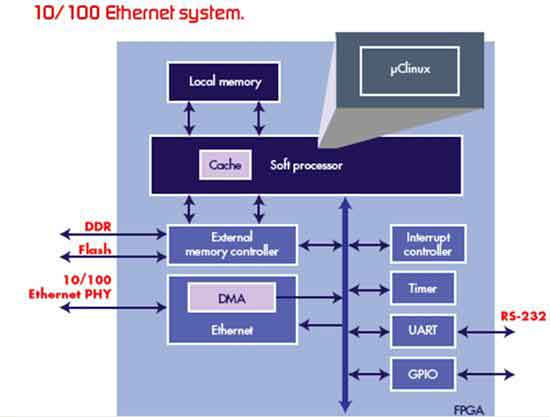

�D4�����͵�10/100��̫�W(w��ng)ϵ�y(t��ng)�ܘ�(g��u)��

ͨ�^���D3�е���Сϵ�y(t��ng)��һ�����ģ����Ԍ��F(xi��n)����TCP/IP��������(10-50Mbps)�����D(zhu��n)����D4��ʾ�ĸ�����͵�10/100��̫�W(w��ng)��Q��������Ҫ��׃���У�

1. ����̫�W(w��ng)MAC����ֱ�Ӵ惦���L��(DMA)���棬���F(xi��n)�Д��(q��)�ӣ�

2. ��ϵ�y(t��ng)�����ⲿ�惦������̎�������Ӿ��棻

3. ����(f��)�s��TCP/IP������Linux(Clinux)ϵ�y(t��ng)TCP/IP�f(xi��)�h����

������Ҫ100Mbps����TCP/IP���������đ�(y��ng)�ã����Կ��]ӲIP��ܛIP��(n��i)�˷�ʽ�ṩ����ģʽ��̫�W(w��ng)MAC(�D5)����@�ø߶ˑ�(y��ng)������Ҫ��500Mbps���ϵ�������������Ҫ���ɢ/�R��DMA(SGDMA)�ȸ�DMA���g(sh��)���Լ�������(sh��)��(j��)��������(DRE)��У��ж�d (CSO)��FPGAӲ�����������g(sh��)��

��M��ǧ����̫�W(w��ng)�����ߔ�(sh��)��(j��)�����ʵ���������Ҫ�������ܵ�Ƕ��ʽ(Ӳ)̎������FPGA�ό��F(xi��n)�Ŀɶ���ܛ̎�������Լ�����ľ��_��������16Kbitָ��͔�(sh��)��(j��)���档��ܛ��ƽ�_���f��Linux��VxWorks��Integrity��QNX��ܛ��ƽ�_�еĸ�TCP/IP��֧���T���㿽ؐ��У����·�ȹ��ܡ�

����Ӳ����ܛ���ڃ�(n��i)���S�����ض���Ӱ푵�TCP���ܣ����M��Ӱ�ϵ�y(t��ng)TCP�����������@Щ���ذ�����

1. ̎�����������l�ʡ����ܺ;���

a. �l�ʣ�TCP/IP�f(xi��)�hͨ����Ҫ���d�ɏ��Ñ����濽ؐ���f(xi��)�h�����Ƶľ��棬Ȼ���ٌ��俽ؐ����̫�W(w��ng)MAC��FIFO��ȥ���@Щ�惦����ؐ������Щ����ܛ����ʽ��ɵģ������Ҫ̎������̎�����ڡ�ͬ�r̎����߀���cTCPУ�͵�Ӌ�㣬Ӌ���^������Ҫ��������(sh��)��(j��)���Ĵ惦���x���������̎������ϸ���Ĵ惦�����ڸ��̵ĕr�g��(n��i)����@Щ�������Ķ����Ա����^�ߵĔ�(sh��)��(j��)���ʣ�

b. ���ܣ�TCP/IP�f(xi��)�h����Ҫ����(sh��)��(j��)���İ��^���d���M���L��̎����������^̎����һ���֣����͵��L�������xȡ���^��Ϣ���ض�λ�����ÿ����(sh��)��(j��)����̎���^�̶���Ҫ�ஔ(d��ng)�����λ������������̎��ÿ����(sh��)��(j��)���r����Ҫ�M�г˷��������ڿ����õ�̎�����У�����_�������λ��˷���ָ����ܫ@�ø��ߵ����ܣ�

c. ���棺��(sh��)��(j��)������̫�W(w��ng)MAC����ؐ���惦����֮����ͨ�^TCP/IP�f(xi��)�h���IJ�ͬ�ӡ�Ȼ��TCP/IP���еĔ�(sh��)��(j��)��̎�����a������(zh��)�С������д��a�͔�(sh��)��(j��)���x�������Е�������̎����Ч�ʲ������̫�W(w��ng)������

2. �惦��

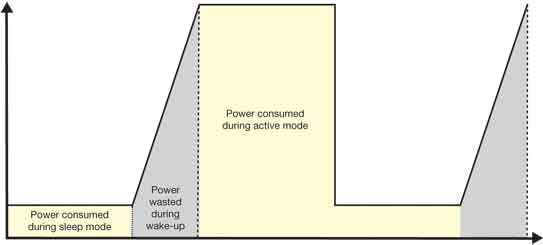

�惦���L���r�g�����t����ϵ�y(t��ng)�����о��Ӱ푡����͑�(y��ng)���У�TCP/IP��(y��ng)�ò����惦�ڱ��ش惦���У�����͔�(sh��)��(j��)�惦���ⲿ�惦���С���ȡ��(sh��)��(j��)��ָ�������M�ĕr�g���������кܴ�Ӱ푡��惦������ͨ���c�����С���P(gu��n)�����ָ��͔�(sh��)��(j��)�����С�����ڜp�p�ⲿ�惦�����t�ʹ�ȡ�r�g��������Ӱ푡�

3. ��̫�W(w��ng)MAC

��FPGA�Ќ��F(xi��n)����̫�W(w��ng)MAC���O(sh��)�ṩ�˺ܴ���`���ԣ��e���ڹ���ģʽ(�oDMA�cSGDMA)����(sh��)��(j��)��FIFO��ȡ�DRE֧�֡�CSO֧���Լ�����֧�ַ��档ÿһ헶���Ӱ푵�MAC����Ҫ���YԴ���Լ����܉��̎���������Ĺ��ܶ��٣��Ķ������w�������Ӱ푡�

4. TCP/IP�f(xi��)�h��

�`��ă�(y��u)��TCP/IP�f(xi��)�h����Ӱ�ϵ�y(t��ng)���ܵ���Ҫ���ء���Ӳ��CSO���㿽ؐAPI(��(sh��)��(j��)����Ҫ�đ�(y��ng)�ÿ�ؐ���f(xi��)�h������)�Լ������×��x헵�TCP/IP�����ܵ�֧�ֿɎ������ϵ�y(t��ng)���ܡ�

5. ��Ϣ����

��Ϣ(��(y��ng)�Ô�(sh��)��(j��))�Ĵ�С��Ӱ����ܵ���һ�����ء��S����Ϣ�p�٣�TCP/IP�f(xi��)�h�^(��TCP��IP����̫�W(w��ng)�^)���_�N���ӣ��Ķ����pС���w�Ĕ�(sh��)��(j��)�d������������

�����(sh��)��(y��ng)�Ì��ڳɱ������ܺ��ܶ���һ�M����������(d��ng)���ض���(y��ng)���O(sh��)Ӌ�a(ch��n)Ʒ�r���O(sh��)Ӌ�ˆT������@Щ����֮�g�M�����_�����ԣ�Ȼ���������m��(y��ng)�Ј��l�����@ЩҪ���ڮa(ch��n)Ʒ�������ڃ�(n��i)���ܕ��l(f��)��׃���������`������õ�ƽ�_�܉��ڲ���׃�O(sh��)Ӌƽ�_��(y��ng)�̵���r�¸���(j��)��Ҫ���@ЩҪ���M������ƽ�⡣�ݣ�Դ��늣��ӣ��W(w��ng)�������ṩ���g(sh��)֧��

���ĵ�ַ��http://www.189yp.com/dz/22/15469290073071.shtml

����(bi��o)��:

-

����FPGA�������F(xi��n)���l�I���{(di��o)���·���O(sh��)Ӌ�ͷ�����C��

����FPGA�������F(xi��n)���l�I���{(di��o)���·���O(sh��)Ӌ�ͷ�����C��

��(sh��)����̖��ݔϵ�y(t��ng)�֞������ݔϵ�y(t��ng)���l����ݔϵ�y(t��ng)���l����ݔϵ�y(t��ng)Ҳ�Д�(sh��)���{(di��o)��ϵ�y(t��ng)����(sh��)���{(di��o)����̖�ַQ���I����̖����(sh��)���{(di��o)���^����̎�����ǔ�(sh��)����̖�����d����������l�ʺ���

�P(gu��n)�I�~�� ���ٙ�Ŀ���O(sh��)Ӌ���� -

��Ξ�Ƕ��ʽϵ�y(t��ng)�x������ĵ�������

��Ξ�Ƕ��ʽϵ�y(t��ng)�x������ĵ�������

�O(sh��)Ӌ����MCU�������ף�Ҳ�]�О������ض�Ƕ��ʽ�O(sh��)Ӌ�x����m��MCU���S���ض��ڑ�(y��ng)�õ�ע����헶��������ã��@ʹ�ñ��^MCUҎ(gu��)�����������(zh��n)�ԡ����ķ������ڷ���������MCU��

�P(gu��n)�I�~�� ���ٙ�Ŀ���O(sh��)Ӌ���� -

��Ԕ��(x��)��FPGAоƬ���x(�D��)

��Ԕ��(x��)��FPGAоƬ���x(�D��)

���գ���ý�w����Q��������Ӽ��g(sh��)�о�����ǰ�ɹ����Ƴ�����(n��i)�ׂ������ɿص����ǧ�f�T�������ܸ߿ɿ�FPGA���F(xi��n)���ɾ����T��У�оƬ��FPGAһֱ�LJ���(n��i)�Ķ̰壬�Ј�������

�P(gu��n)�I�~����Ƭ�C ���ٙ�Ŀ���O(sh��)Ӌ���� -

Ƕ��ʽϵ�y(t��ng)�Ĺ���ԭ���͑�(y��ng)��

Ƕ��ʽϵ�y(t��ng)�Ĺ���ԭ���͑�(y��ng)��

Ƕ��ʽϵ�y(t��ng)�Ĺ���ԭ���͑�(y��ng)�á���Ӌ��C����20���o(j��)���������İl(f��)��֮һ������Ҳ���~���PC�r������PC�r���ĵ���Ҳ��(bi��o)־��Ƕ��ʽ�a(ch��n)Ʒ���Q�������֙C��PDA����(sh��)�ؙC���ȡ�

�P(gu��n)�I�~��Ƕ��ʽϵ�y(t��ng)��Ƭ�C ���ٙ�Ŀ���O(sh��)Ӌ���� -

Ƕ��ʽ�R���Z�ԌW(xu��)��(x��)��(j��ng)�

Ƕ��ʽ�R���Z�ԌW(xu��)��(x��)��(j��ng)�

������c��һ���Ŀ����Ҫ��Ƕ��ʽ�R�����yԇ���R������?q��)��^��C����Ҳ���^�����nj�����������팑߀�ǵ�һ�Σ���ȫ�]�и��ֻ���ϾW(w��ng)���Y�ϣ��Լ����������������Լ�һ

�P(gu��n)�I�~�� ���ٙ�Ŀ���O(sh��)Ӌ���� -

Մ?w��)�Ƕ��ʽϵ�y(t��ng)�����c����Ԕ��(x��)��B

Մ?w��)�Ƕ��ʽϵ�y(t��ng)�����c����Ԕ��(x��)��B

�o

�P(gu��n)�I�~��Ƕ��ʽϵ�y(t��ng)��Ƭ�C ���ٙ�Ŀ���O(sh��)Ӌ���� -

ʲô��Ƕ��ʽϵ�y(t��ng)��ʮ����

ʲô��Ƕ��ʽϵ�y(t��ng)��ʮ����

�o

�P(gu��n)�I�~��Ƕ��ʽϵ�y(t��ng)��Ƭ�C ���ٙ�Ŀ���O(sh��)Ӌ���� -

��BJavaǶ��ʽϵ�y(t��ng)�_�l(f��)

��BJavaǶ��ʽϵ�y(t��ng)�_�l(f��)

�o

�P(gu��n)�I�~��Ƕ��ʽϵ�y(t��ng)��Ƭ�C ���ٙ�Ŀ���O(sh��)Ӌ���� -

Ƕ��ʽϵ�y(t��ng)|Ƕ��ʽLinux�_�l(f��)����

Ƕ��ʽϵ�y(t��ng)|Ƕ��ʽLinux�_�l(f��)����

�o

�P(gu��n)�I�~��Ƕ��ʽϵ�y(t��ng)��Ƭ�C ���ٙ�Ŀ���O(sh��)Ӌ���� -

Ƕ��ʽܛ���_�l(f��)|�l(f��)չڅ��

Ƕ��ʽܛ���_�l(f��)|�l(f��)չڅ��

�o

�P(gu��n)�I�~��Ƕ��ʽϵ�y(t��ng)��Ƭ�C ���ٙ�Ŀ���O(sh��)Ӌ���� -

ʲô��Ƕ��ʽϵ�y(t��ng)

ʲô��Ƕ��ʽϵ�y(t��ng)

�o

�P(gu��n)�I�~��Ƕ��ʽϵ�y(t��ng)��Ƭ�C ���ٙ�Ŀ���O(sh��)Ӌ���� -

Ƕ��ʽϵ�y(t��ng)Ԕ��(x��)��B

Ƕ��ʽϵ�y(t��ng)Ԕ��(x��)��B

�o

�P(gu��n)�I�~��Ƕ��ʽϵ�y(t��ng)��Ƭ�C ���ٙ�Ŀ���O(sh��)Ӌ���� -

����Ƕ��ʽϵ�y(t��ng)|�����~�R��2

����Ƕ��ʽϵ�y(t��ng)|�����~�R��2

�o

�P(gu��n)�I�~��Ƕ��ʽϵ�y(t��ng)��Ƭ�C ���ٙ�Ŀ���O(sh��)Ӌ���� -

����Ƕ��ʽϵ�y(t��ng)|�����~�R��1

����Ƕ��ʽϵ�y(t��ng)|�����~�R��1

�o

�P(gu��n)�I�~�� ���ٙ�Ŀ���O(sh��)Ӌ����

������dȤ��

- ���]��(n��i)��

- ����(n��i)��

-

- �oԴ�����x�� 2024-10-10

- ACM6755 ֧��3������(y��ng)�õ�ȫ��������ֱ���oˢ늙C�(q��)��IC���� 2024-10-09

- YXC�����Q�����������I(y��)���C��(y��ng)�� 2024-09-27

- ��Դ����͟oԴ����ą^(q��)�e 2024-09-24

- ��ģ�K��Ȳ��p����ѕr�lCP-��־��� 2024-09-20

- ���w�C�����Ĺ���ԭ�� 2024-09-19

- YXCʯӢ��Դ��ֿɾ��̾����l�c200MHZ��С��(sh��)�c�ɾ��_����6λ����(y��ng)����5G��վ 2024-09-12

- 70V�͉����{(di��o)OVP�ֵ���^�����oо-ƽоPW1600 2024-09-05

- YXC�P�d��Դ��Ʒ�l(f��)��ح1.2V�����ĕr犽�Q���� 2024-09-05

- YXC�P�d | 32.768KHZ�����x�ͷ��� 2024-09-02

- ���T��(bi��o)��

-

���ż����· ������·�D LED ���l�Ŵ����·�D ��Ƭ�C 늙C���� LED�·�D ��(w��n)���Դ �_�P(gu��n)��(w��n)���Դ ����·�D ׃�l�� ��׃�� LED�����· ���{(di��o)�S���g(sh��) LED�(q��)���·�D AV�Ŵ����· �ص����·�D 555���r�� 늴Št�·�D ��(w��n)�������· 51��Ƭ�C �·�O(sh��)Ӌ �^�����o�· �^�����o�· ��(w��n)���· �ھ�Ӌ�� ���˷�(w��n)���· ��·���o�· �ŷ�늙C ���M늙C PIC��Ƭ�C ֱ����(w��n)���Դ ���{(di��o)��(w��n)���Դ EMC ©늱��o�· Ƕ��ʽϵ�y(t��ng) ��Ȧ ���l��׃�� ���� ���{(di��o) UPS DC-DC�· �ضȂ����� 늴ż��� ���� ���l�_�P(gu��n)�Դ ���� EMI ��˹�� ���⾀